- トップページ

- >

- グロースのシゴト

- >

- 事例3

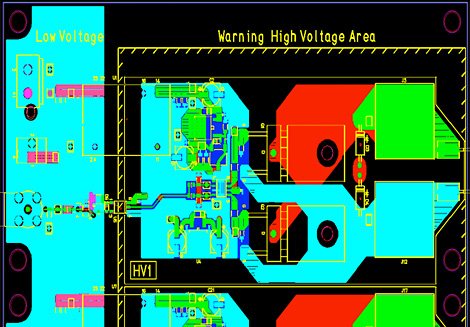

[事例2]高電圧基板のアートワーク+基板作製

初めて高電圧基板を開発するお客様からご相談を受け、弊社主体で基板設計値などのご提案をさせて頂きました。

高電圧基板での空間距離(※1)、沿面距離(※2)は、

・ 各国の規格(JIS、IECなど)

・ 過電圧カテゴリと動作電圧

・ 汚染度

・ 絶縁材料(CTI値)

などによって決まりますが、

本基板では、遵守すべき規格は明確には無いケースだった為、機能、性能、安全性を満足するように、弊社主体で提案を行い、お客様と調整のうえ、

JIS C1010-1 表7 沿面距離

汚染度2、CTI値175以上より、

他ブロック間:10mm

Low-Highブロック間:フォトカプラ部を除き、13.6mm

と決定しました。

出力部FETは、

並列接続のため、配線インダクタンスが同等になるように、対称な配置・配線にしています。

また、フォーミングを行い、ドレイン及びソースと他pinの空間距離を確保するようにしました。

![]()

※1、※2 )空間距離、沿面距離とは

測定、制御及び研究室用機器の空間距離及び沿面距離は、JIS C1010等で規定されています。

空間距離 : 2つの導電性部分間の、空間を通る最短距離

沿面距離 : 2つの導電性部分間の、絶縁物の表面に沿った最短距離