アナログの概念をデジタルの領域に持ち込んだボード設計

当社では、高速なシステム速度を実現するため、アナログの概念をデジタル領域に持込んだボード設計を行っています。具体的に注力しているポイントをご紹介します。

![]()

![]()

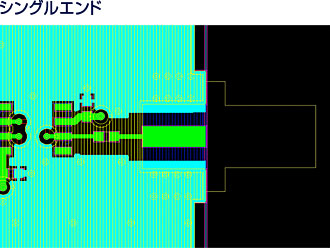

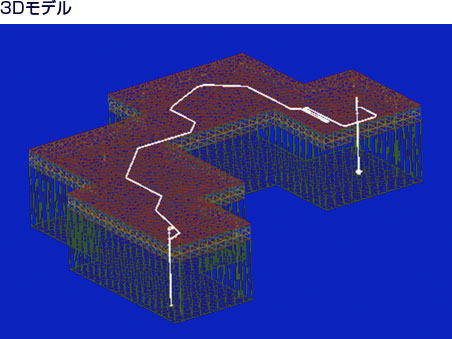

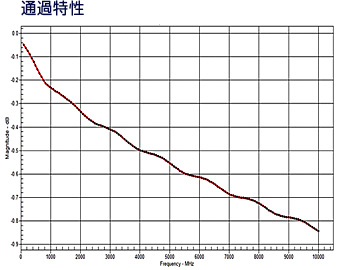

基板における不連続性を回避し【信号劣化】を防ぎます

主にSMA部分におけるインダクタンスの不連続性、主にコネクタ部分におけるキャパシタンスの不連続性、主にビアや直角曲げによる伝送線路の不連続性などを回避し信号の劣化を防ぎます。

![]()

![]()

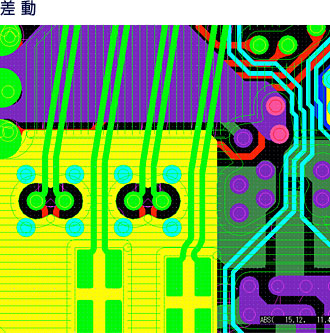

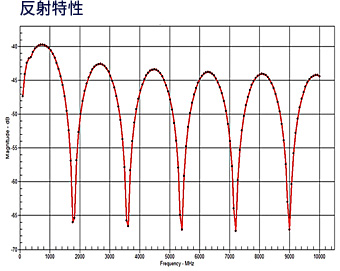

終端の最適配置と方法をご提案し【反射】を防ぎます

適切に終端されていないデータラインやクロックラインなどの伝送線路は、信号が反射してしまいます。終端位置や終端方法を適切に選択し、部品点数の増加を防ぎつつ効果的な反射防止策をご提案することが可能です。

![]()

![]()

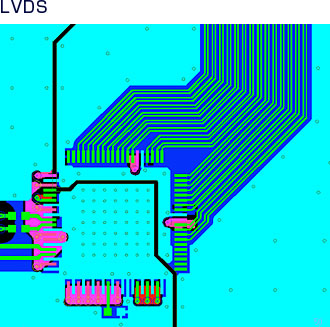

【クロストーク】を回避します

高速の並列バス信号以外で、平行する配線どおしの影響を無くすことに主眼を置いたボードレイアウトを行います。誘導性クロストーク、容量性クロストークの発生原因は異なりますが、ボード上では両者とも同じ対策方法が有効となりますので、クロストークの回避が可能です。

![]()

![]()

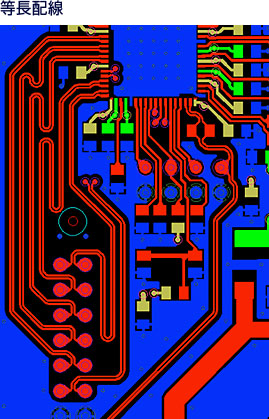

【グランドバウンス】を起こさないボードレイアウトを行います

大規模FPGAやLSIに含まれる数百のI/Oピンが高速にHighからLowに切替わることで、電源電圧が非常に不安定になり、安定的な電力リファレンスを得ることが出来なくなります。

適切かつ綿密なボードレイアウトを行うことでこの問題を回避致します。

例:マイクロストリップ

コプレナー無

シングル

W= mm

f=Mhz

t=μm

εr(比誘電率)=

h=mm

Ω

![]()

l=mm

W=mm

t=μm

nH

![]()

同一面で隣接するGNDなどは省略する。

l=mm

W=mm

εr(比誘電率)=

h=mm

pF

![]()

t=μm

l=mm

W=mm

温度℃

mΩ

![]()

εr(比誘電率)=

ps/mm